A companhia sul-coreana deve liderar a indústria em busca da tecnologia para a fabricação de processadores de até 4 nm

A Lei de Moore é uma constatação de George Moore, cofundador da Intel, que afirma que o número de transistores em um chip dobra a aproximadamente a cada dois anos mantendo o mesmo custo. Feita em 1965, essa afirmação vem sendo concretizada com maior ou menor precisão, apesar de o próprio Moore já ter declarado que essa regra tende a parar de funcionar.

Contrariando essa previsão de morte da Lei de Moore, a Samsung revelou ontem (24) seus planos para o futuro dos semicondutores, que devem ser colocados em prática a partir de julho. Após ter sido a primeira empresa a lançar chips de 14 nm e 10 nm, a companhia sul-coreana deve liderar a indústria em busca da tecnologia para a fabricação de processadores de até 4 nm, segundo foi revelado.

Painel do Samsung Foundry Forum 2017

Painel do Samsung Foundry Forum 2017

Fundição eletrônica do futuro

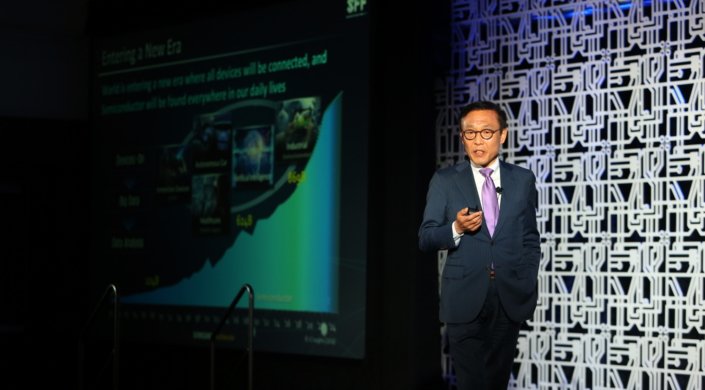

O anúncio do que chamaram de “roteiro da tecnologia de processo de fundição abrangente” detalhou como a empresa pretende ajudar clientes a projetar e fabricar chips mais eficientes. Tudo foi feito no Samsung Foundry Forum 2017 com apresentação de Kinam Kim, presidente da área de semicondutores da Samsung Electronics.

A tecnologia para 8 nm Low Power Plus (LPP) é a mais competitiva antes da mudança para a litografia EUV

As informações reveladas no fórum dizem respeito a processos para a criação de chips de 8 nm, 7 nm, 6 nm, 5 nm e até 4 nm, menos da metade do que se fabrica hoje. A tecnologia para 8 nm Low Power Plus (LPP) é a mais competitiva antes da mudança para a litografia EUV (extreme ultra violet, ou ultravioleta extremo). Ela vai usar processos e inovações da tecnologia de 10 nm da Samsung.

Já a tecnologia de 7 nm LPP vai estrear a litografia EUV para criar semicondutores menores e eficientes. O processo para 6 nm vai usar a solução de dimensionamento exclusiva da Samsung, assim como para 5 nm.

Kinam Kim, presidente da área de semicondutores da Samsung Electronics

Kinam Kim, presidente da área de semicondutores da Samsung Electronics

Dando um passo à frente

A inclusão dessas tecnologias de processo permitirá uma explosão de novos dispositivos que conectarão os consumidores

A primeira implementação da próxima geração de arquitetura de dispositivos vai surgir na forma dos chips de 4 nm, com estrutura MBCFET (Multi Bridge Channel FET). Para superar o dimensionamento físico e as limitações de performance da arquitetura FinFET (a estrutura atual de chips), a Samsung vai usar a tecnologia GAAFET (Gate All Around FET), que utiliza um dispositivo Nanosheet.

Jong Shik Yoon, vice-presidente executivo da área de fundição eletrônica da Samsung Electronics, afirmou que “o roteiro avançado de tecnologia de processo da Samsung Foundry é um testemunho da natureza colaborativa de nossos relacionamentos com parceiros, clientes e ecossistemas. A inclusão dessas tecnologias de processo permitirá uma explosão de novos dispositivos que conectarão os consumidores de maneiras nunca antes vistas”.

Fontes

Categorias

![Imagem de: Home office: 52 vagas para trabalho remoto internacional [24/04]](https://tm.ibxk.com.br/2025/04/24/24084535470004.jpg?ims=288x165)